The USC Stevens Center for Innovation has licensed a set of technologies developed at the University of Southern California to Optimal IC Technologies Inc., a Colorado-based startup company focused on optimization of semiconductor designs in pre- and post-production phases of manufacturing. Optimal IC Technologies plans to develop and market products based on the patented USC discoveries for testing and simulating integrated circuits (ICs), the building blocks of computerized electronics.

“The technologies we’ve licensed from USC have huge potential for improving semiconductor manufacturing yields,” said Lewis Hartle, chief executive officer of Optimal IC Technologies. “What’s more, they enable manufacturers to optimize a given chip design for performance or power consumption depending upon the application of the chip. We intend to develop products that help semiconductor manufacturers improve yields while maximizing the performance and power potentials of their designs.”

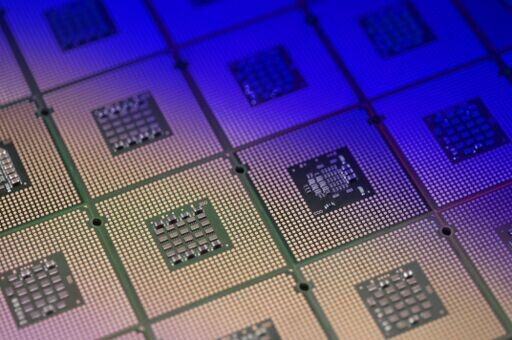

ICs, also known as semiconductor chips or simply “chips,” are used in virtually every electronic device or appliance sold today, from personal computers and smartphones to refrigerators, vending machines and automobiles. ICs are tiny complex assemblies of electronic circuitry etched onto semiconductor material, usually silicon, before they are encased in (typically) plastic packaging to perform the applications they are designed for. Such chips range from the complex multi-core microprocessors in central processing units (CPUs) that are the “brains” of today’s laptop, desktop and supercomputers, to graphics processors, logic chips and random-access memory chips (i.e., DRAM).

All such chips are prone to power and performance issues in spite of design verifications that are routinely performed just prior to production. These issues involve “hotspot” variances within a given chip’s design that adversely affect the operation of the entire chip. Such hotspots, which can appear in different chips of the same design in different locations, have variances in thresholds of tolerance to routine voltages applied during testing. When those thresholds are exceeded, the excessive heat will ruin chips during testing, reducing all-important production yields. These hotspots also cause inefficiencies that can make a chip underperform. Optimal IC is working to develop products that easily scan or “map” IC circuitry prone to hotspots in the design validation phase, pre-production. Additional products will focus on post-packaging tests that enable each chip to be similarly scanned, mapped and tuned to operate within the thresholds of tolerance dictated by a given hotspot, reducing failures while improving performance or power consumption.

“This technology from USC has incredible potential to revolutionize IC design quality assurance testing of several types of mass-market chips,” Hartle said. “Any improvement to semiconductor production yields has a direct, positive impact on profits for IC manufacturers. Better yield simply means greater profits. The beauty of it is that while hotspot thresholds can be easily identified to reduce failures, the entire IC can also be tuned to emphasize performance, power savings, or both by using the same high-resolution circuit visibility this technology is capable of.”

Optimal IC’s products will also leverage the licensed technology to improve computer system security. It can do so by scanning the tiny subcomponents and circuits on a chip-by-chip basis to identify hardware and software vulnerabilities inadvertently or maliciously introduced by a third-party fabrication company. Many so-called “fabless” semiconductor companies choose to rely upon other companies to be their outsourced means of production. The technology also has the potential to allow systems manufacturers (makers of phones, laptops, servers and embedded computing systems) to differentiate by offering the means to easily identify back-door hacking activity before a malicious breach can occur.

USC Professor Young Cho led the research team at the USC Viterbi School of Engineering Information Sciences Institute to develop the patented USC technologies licensed to Optimal IC. One of the core advancements of Cho’s research was in improving the ability to measure the power used by electronic circuits at a sub-component level, which allows chips to be tested without using the processing power of the chip itself – something that has never been done before.

“Young Cho’s research is an exciting development for semiconductor design and production,” said Michael Arciero, director of technology licensing and new ventures at the USC Stevens Center. “It has the potential to dramatically impact the chip manufacturing sector.”

In 2017, Professor Cho earned a $50,000 Technology Advancement Grant (TAG) from the USC Stevens Center for Innovation to further develop one of a suite of technologies licensed to the semiconductor company. These grants support early-stage technologies invented at USC through validation or proof-of-concept development. The $50,000 grant helped Cho and his team purchase hardware to validate that the technology worked as designed. Prior to the TAG funding, Cho received National Science Foundation (NSF) funding support.